인공지능(AI) 산업이 모델을 만드는 ‘학습’ 단계에서 실제 서비스에 활용하는 ‘추론’ 단계로 무게중심을 옮기면서, 메모리 기술의 대전환이 예고되고 있다. 특히 GPT-4와 같은 초거대 언어모델은 파라미터 수가 1조 8천억 개에 달해 약 3.6TB의 메모리 용량이 필요하지만, 현재 최고 사양 GPU인 NVIDIA H200도 141GB에 불과해 물리적 한계에 직면한 상황이다.

이에 따라 고대역폭 메모리(HBM)의 속도와 낸드 플래시의 대용량을 결합한 ‘High Bandwidth Flash(HBF)’가 차세대 게임 체인저로 부상하고 있다. 2026년 2월 현재 업계에서는 HBF를 통해 AI 추론 서버의 메모리 병목 현상을 해소할 수 있을 것으로 기대하고 있다.

속도와 용량, 두 마리 토끼 잡는 기술

기존 메모리 구조에서 HBM은 대역폭이 1.44TB/s로 빠르지만 용량이 작고 가격이 비싸다. 반면 SSD는 용량이 수십 TB로 크지만 대역폭이 수 GB/s 수준으로 HBM 대비 수백 배 느리다. HBF는 이 두 기술 사이의 거대한 간극을 메우는 역할을 한다.

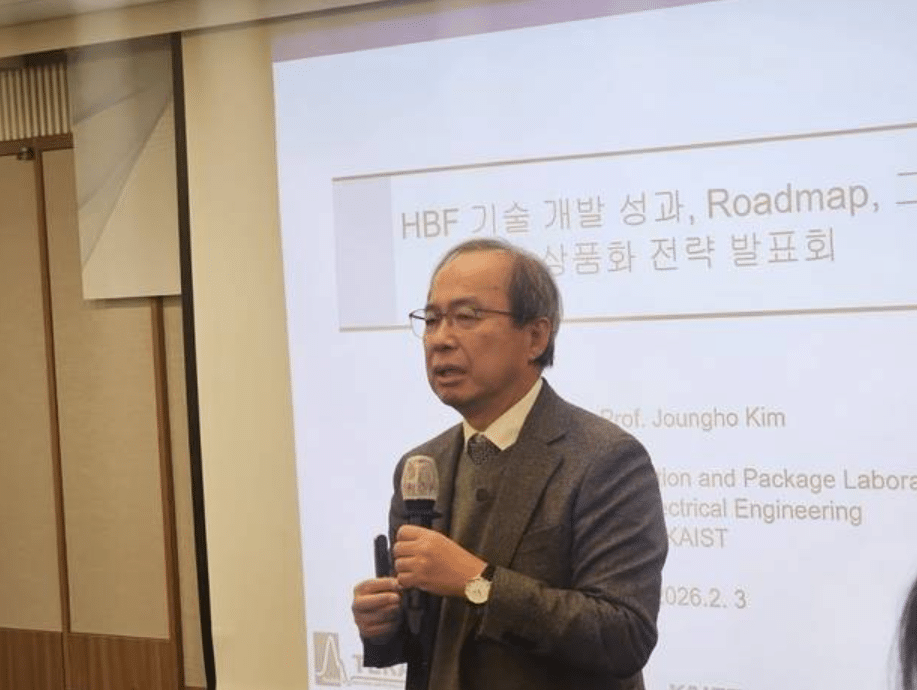

KAIST 김정호 교수는 이를 “HBM은 자주 보는 책을 꽂아둔 책꽂이, HBF는 방대한 지식을 보관하는 도서관”에 비유하며, AI 추론 단계에서는 학습된 거대한 파라미터 데이터를 저장하고 읽어내는 용량과 대역폭이 동시에 요구된다고 설명했다.

HBF는 목표 대역폭 1.6TB/s 이상에 용량은 4TB 이상을 제공하는 것을 목표로 한다. 또한 낸드 플래시 기반이라 전원을 꺼도 데이터가 유지되는 비휘발성을 가지며, D램처럼 리프레시 동작이 필요 없어 전력 효율도 뛰어나다.

실리콘 관통 전극으로 16층 이상 적층

HBF의 핵심 기술은 TSV(Through-Silicon Via), 즉 실리콘 관통 전극이다. 기존 낸드 패키징 방식 대신 TSV를 사용해 16층 이상의 낸드 칩을 수직으로 적층하고 전기적 이동 경로를 최소화한다. 이는 2012년 AMD HBM에서 처음 상용화된 기술로, 현재 HBM3E에서 고도화되어 적용 중이다.

최하단에 위치한 로직 다이는 단순 입출력 제어를 넘어 수천 개의 채널을 동시에 관리하고 에러 정정 및 웨어 레벨링을 수행하는 고성능 프로세서 역할을 한다. 시뮬레이션 결과 LLAMA 3.1 405B 모델 추론 시 HBF는 무제한 용량의 HBM 대비 약 2.2%의 성능 차이만 보인 것으로 나타났다.

표준화와 상용화는 진행형… 업계는 신중

글로벌 시장조사기관 가트너는 2025년 보고서에서 “AI 메모리 계층의 다층화는 필연적”이라며 HBF와 같은 기술의 필요성을 인정했다. 삼성전자는 2024년 6월 ‘Advanced Memory Architecture’ 발표를 통해 관련 연구를 시사했고, JEDEC은 2025년 3월 HBF 표준화 작업 그룹을 신설한 것으로 알려졌다.

다만 업계 관계자들은 낸드의 낮은 내구성과 레이턴시 한계, TSV 16층 이상 적층 시 수율 문제 등을 우려하고 있다. 반도체 애널리스트들은 “HBF가 기술적으로 타당하더라도 2026년 상반기 기준 아직 상용화 전 단계”라며 “실제 시장 영향을 분석하려면 주요 제조사의 공식 입장과 표준화 완료 시기를 지켜봐야 한다”고 분석했다.

한편 HBF가 본격 양산될 경우 D램 기반 HBM 수요 성장률이 둔화되고 NAND는 고부가 시장에 진입하는 등 메모리 공급망 재편이 예상된다. 업계에서는 HBF와 HBM이 고급 패키징 공정을 공유해 공급 병목이 발생할 가능성도 제기되고 있다.